NNT: 2016SACLS285

# Thèse de doctorat de l'Université Paris-Saclay préparée Université Paris-Sud

Ecole doctorale n°580 Sciences et technologies de l'information et de la communication Spécialité de doctorat : Informatique

par

# M. Ian Masliah

Méthodes de génération automatique de code appliquées à l'algèbre linéaire numérique dans le calcul haute performance

Thèse présentée et soutenue à Gif-Sur-Yvette, le 26 septembre 2016.

#### Composition du Jury:

| M. E | Emmanuel Chailloux | Professeur                       | (Président du jury)     |

|------|--------------------|----------------------------------|-------------------------|

|      |                    | Université Pierre et Marie Curie |                         |

| M. F | Paolo Bientinesi   | Professeur                       | (Rapporteur)            |

|      |                    | Aachen University                |                         |

| M. I | David Hill         | Professeur                       | (Rapporteur)            |

|      |                    | Université Blaise Pascal         |                         |

| M. F | Frédéric Magoulès  | Professeur                       | (Examinateur)           |

|      |                    | Ecole Centrale Paris             |                         |

| M. N | Marc Baboulin      | Professeur                       | (Directeur de thèse)    |

|      |                    | Université Paris-Sud             |                         |

| M. J | Joël Falcou        | Maître de Conférences            | (Co-Directeur de thèse) |

|      |                    | Université Paris-Sud             |                         |

Titre : Méthodes de génération automatique de code appliquées à l'algèbre linéaire numérique dans le calcul haute performance

**Keywords :** programmation générique, DSELs, programmation générative, C++, algèbre linéaire, GPU

**Résumé :** Les architectures parallèles sont aujourd'hui présentes dans tous les systèmes informatiques, allant des smartphones aux supercalculateurs en passant par les ordinateurs de bureau. Programmer efficacement ces architectures en fonction des applications requiert un effort pluridisciplinaire portant sur les langages dédies (Domain Specific Languages - DSL), les techniques de génération de code et d'optimisation, et les algorithmes numériques propres aux applications.

Dans cette thèse, nous présentons une méthode de programmation haut niveau prenant en compte les caractéristiques des architectures hétérogènes et les propriétés existantes des matrices pour produire un solveur générique d'algèbre linéaire dense. Notre modèle de programmation supporte les transferts explicites et implicites entre un processeur (CPU) et un processeur graphique qui peut être généraliste (GPU) ou intégré (IGP). Dans la mesure où les GPU sont devenus un outil important pour le calcul haute performance, il est essentiel d'intégrer leur usage dans les plateformes de calcul. Une architecture récente telle que l'IGP requiert des connaissances supplémentaires pour pouvoir être programmée efficacement. Notre méthodologie a pour but de simplifier le développement sur ces architectures parallèles en utilisant des outils de programmation haut niveau. À titre d'exemple, nous avons développé un solveur de moindres carrés en précision mixte basé sur les équations semi-normales qui n'existait pas dans les bibliothèques actuelles.

Nous avons par la suite étendu nos travaux à un modèle de programmation multi-étape ("multi-stage") pour résoudre les problèmes d'interopérabilité entre les modèles de programmation CPU et GPU. Nous utilisons cette technique pour générer automatiquement du code pour accélérateur à partir d'un code effectuant des opérations point par point ou utilisant des squelettes algorithmiques. L'approche multi-étape nous assure que le typage du code généré est valide. Nous avons ensuite montré que notre méthode est applicable à d'autres architectures et algorithmes. Les routines développées ont été intégrées dans une bibliothèque de calcul appelée NT2.

Enfin, nous montrons comment la programmation haut niveau peut être appliquée à des calculs groupés et des contractions de tenseurs. Tout d'abord, nous expliquons comment concevoir un modèle de container en utilisant des techniques de programmation basées sur le C++ moderne (C++-14). Ensuite, nous avons implémenté un produit de matrices optimisé pour des matrices de petites tailles en utilisant des instructions SIMD.

Title: Automatic code generation methods applied to numerical linear algebra in high performance computing

**Keywords:** Generic programming, DSELs, Generative programming, C++, linear algebra, GPU

Abstract: Parallelism in today's computer architectures is ubiquitous whether it be in supercomputers, workstations or on portable devices such as smartphones. Exploiting efficiently these systems for a specific application requires a multidisciplinary effort that concerns Domain Specific Languages (DSL), code generation and optimization techniques and application-specific numerical algorithms.

In this PhD thesis, we present a method of high level programming that takes into account the features of heterogeneous architectures and the properties of matrices to build a generic dense linear algebra solver. Our programming model supports both implicit or explicit data transfers to and from General-Purpose Graphics Processing Units (GPGPU) and Integrated Graphic Processors (IGPs). As GPUs have become an asset in high performance computing, incorporating their use in general solvers is an important issue. Recent architectures such as IGPs also require further knowledge to program them efficiently. Our method aims at simplifying the development on parallel architectures through the use of high level programming techniques. As an example, we developed a least-squares solver based on semi-normal equations in mixed precision that cannot be found in current libraries. This solver achieves similar performance as other mixed-precision algorithms.

We extend our approach to a new multistage programming model that alleviates the interoperability problems between the CPU and GPU programming models. Our multistage approach is used to automatically generate GPU code for CPU-based element-wise expressions and parallel skeletons while allowing for type-safe program generation. We illustrate that this work can be applied to recent architectures and algorithms. The resulting code has been incorporated into a C++ library called NT2.

Finally, we investigate how to apply high level programming techniques to batched computations and tensor contractions. We start by explaining how to design a simple data container using modern C++-14 programming techniques. Then, we study the issues around batched computations, memory locality and code vectorization to implement a highly optimized matrix-matrix product for small sizes using SIMD instructions. By combining a high level programming approach and advanced parallel programming techniques, we show that we can outperform state of the art numerical libraries.

# Table of contents

| In | trodi | uction |                                                           | 2   |

|----|-------|--------|-----------------------------------------------------------|-----|

| 1  | The   | issue  | of adapting numerical libraries to parallel architectures | 6   |

|    | 1.1   |        | evel Programming for Scientific Computing                 | 7   |

|    | 1.2   | _      | g dense linear systems                                    | 8   |

|    |       | 1.2.1  | LU factorization                                          | 9   |

|    |       | 1.2.2  | QR factorization                                          | l 1 |

|    |       | 1.2.3  | Solvers in LAPACK and MAGMA                               | 12  |

|    |       |        | 1.2.3.1 General solvers                                   | 13  |

|    |       |        | 1.2.3.2 Iterative refinement                              | L4  |

|    |       |        | 1.2.3.3 Mixed precision algorithm                         | L4  |

|    | 1.3   | Archit | sectures: Design and evolution                            | 15  |

|    |       | 1.3.1  | SIMD extensions                                           | 15  |

|    |       | 1.3.2  | Multicore systems                                         | 16  |

|    |       | 1.3.3  | Graphics Processing Units (GPU)                           | ١7  |

|    |       | 1.3.4  | Accelerated Processing Units                              | 19  |

|    | 1.4   | Progra | amming tools and techniques                               | 20  |

|    |       | 1.4.1  | Low-level programming tools                               | 21  |

|    |       |        | 1.4.1.1 SIMD support                                      | 21  |

|    |       |        | 1.4.1.2 Multicore support                                 | 23  |

|    |       |        | 1.4.1.3 Accelerator support                               | 24  |

|    |       | 1.4.2  | Domain Specific Languages                                 | 24  |

|    |       | 1.4.3  | Domain Specific Embedded Languages                        | 25  |

|    |       | 1.4.4  | Multi-stage programming                                   | 26  |

|    | 1.5   | Consid | dered language and library                                | 26  |

|    |       | 1.5.1  |                                                           | 26  |

|    |       | 1.5.2  | The $NT^2$ library                                        | 27  |

|    | 1.6   | Concl  | usion                                                     | 29  |

| 2  | Hig   | h-leve | programming for dense linear algebra 3                    | 80  |

|    | 2.1   |        |                                                           | 31  |

|    | 2.2   | Gener  | ative programming for designing numerical libraries       | 33  |

|    |       | 2.2.1  |                                                           | 33  |

|    |       | 2.2.2  | Generative programming in software development            | 34  |

|    |       | 2.2.3  | 9 9                                                       | 34  |

|    | 2.3   |        |                                                           | 36  |

|    |       | 2.3.1  | *                                                         | 36  |

|    |       | 2.3.2  | 9                                                         | 36  |

|    | 2.4   |        | 9                                                         | 39  |

|    |       | 2.4.1  | Linear system solvers                                     | 39  |

#### Table of contents

|    |       | 2.4.2<br>2.4.3 | Memory management for hybrid computation                | 42<br>43  |

|----|-------|----------------|---------------------------------------------------------|-----------|

|    | 2.5   |                | sion                                                    | 51        |

| 3  | Mul   | _              | ge programming in C++ for GPGPUs                        | <b>52</b> |

|    | 3.1   |                | d Work                                                  | 53        |

|    | 3.2   | Multi-         | stage programming in C++                                | 56        |

|    |       | 3.2.1          | Designing a multi-stage software                        | 56        |

|    |       | 3.2.2          | Multi-stage programming in $C++$                        | 57        |

|    |       | 3.2.3          | Multi-stage programming tool for $NT^2$                 | 58        |

|    | 3.3   |                | are implementation for $NT^2$                           | 59        |

|    | 3.4   | Experi         | iments                                                  | 64        |

|    |       | 3.4.1          | Black & Scholes kernel                                  | 65        |

|    |       | 3.4.2          | Linsolve kernel                                         | 68        |

|    | 3.5   | Conclu         | sion                                                    | 69        |

| 4  | App   |                | on to batched computations and tensor contractions      | 70        |

|    | 4.1   |                | rs in numerical libraries                               | 71        |

|    | 4.2   |                | eations and challenges                                  | 72        |

|    | 4.3   |                | iner concept                                            | 73        |

|    |       | 4.3.1          | C++11/14 features                                       | 74        |

|    |       | 4.3.2          | Developing a tensor interface                           | 79        |

|    | 4.4   | _              | izing small matrix-matrix products                      | 81        |

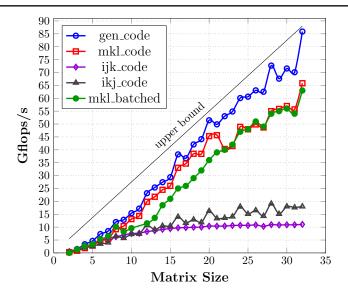

|    |       | 4.4.1          | Performance measures                                    | 81        |

|    |       | 4.4.2          | Data Access Optimizations and Loop Transformation Tech- |           |

|    |       |                | niques                                                  | 82        |

|    |       | 4.4.3          | Register Data Reuse and Locality                        | 83        |

|    |       | 4.4.4          | Algorithmic Advancements                                | 84        |

|    |       | 4.4.5          | Effect of the Multi-threading                           | 86        |

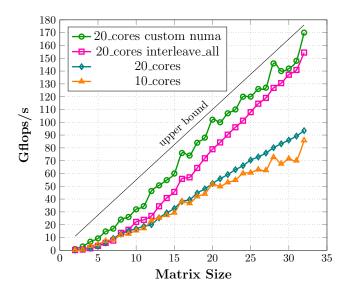

|    |       | 4.4.6          | Effect of the NUMA-socket and Memory Location           | 87        |

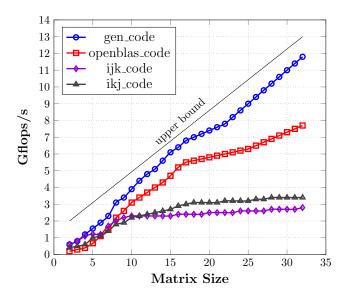

|    |       | 4.4.7          | Application to ARM processor                            | 88        |

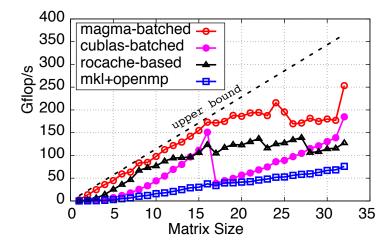

|    |       | 4.4.8          | Efficient wrapper for GPU batched GEMM                  | 88        |

|    | 4.5   | Conclu         | sion                                                    | 90        |

| Co | onclu | sion a         | nd Perspectives                                         | 92        |

| Bi | bliog | graphy         |                                                         | 94        |

# List of Figures

| 1.1 | SIMD concept                                                               | 15 |

|-----|----------------------------------------------------------------------------|----|

| 1.2 | Multicore concept                                                          | 16 |

| 1.3 | NUMA concept                                                               | 17 |

| 1.4 | GPU Kepler based architecture                                              | 18 |

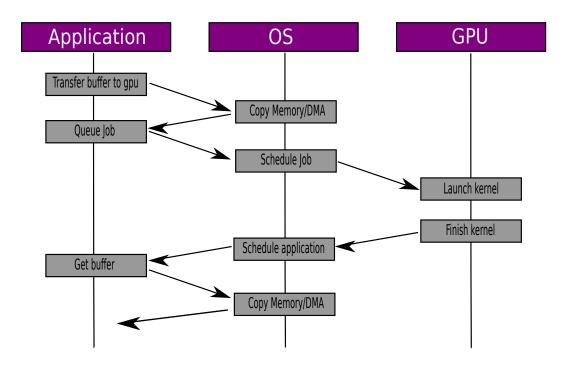

| 1.5 | Work flow for a GPU                                                        | 19 |

| 1.6 | IGP architecture                                                           | 20 |

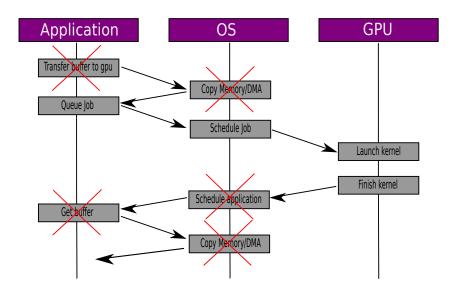

| 1.7 | Work flow for a zero copy IGP                                              | 21 |

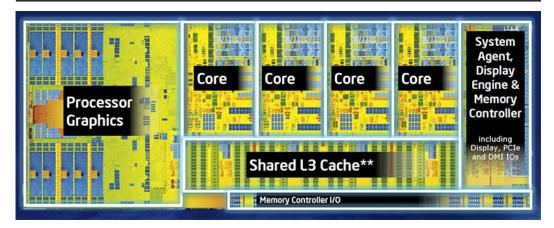

| 1.8 | Intel's 3rd generation IGP architecture                                    | 22 |

| 1.9 | Expression Templates in $NT^2$                                             | 28 |

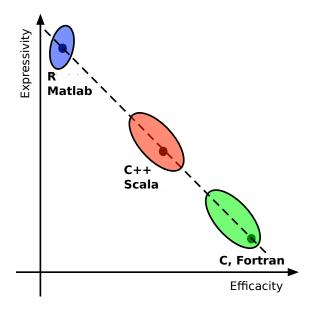

| 2.1 | Abstraction/Efficiency trade-off for languages                             | 32 |

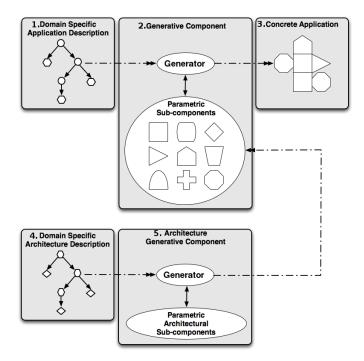

| 2.2 | Overview of the $NT^2$ skeleton based generation process                   | 35 |

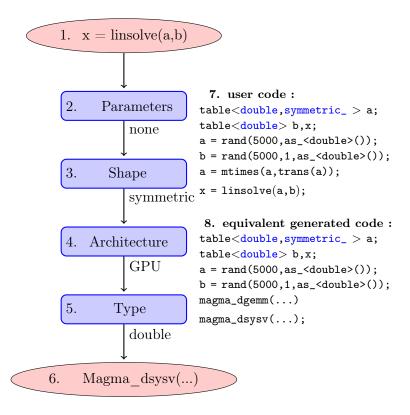

| 2.3 | Example of a generation process for a symmetric system                     | 41 |

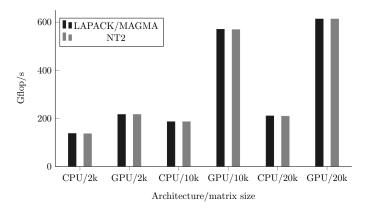

| 2.4 | Performance comparison between LAPACK/MAGMA routines and                   |    |

|     | generated codes via $NT^2$ for general dense linear system solution        | 43 |

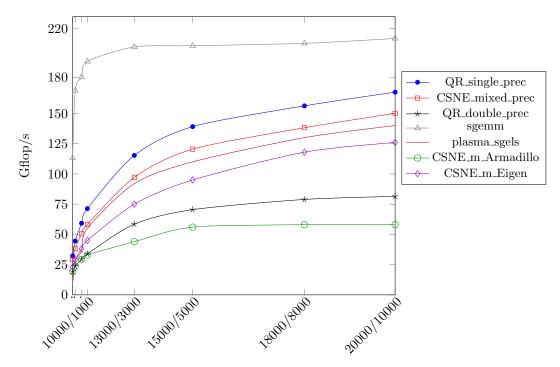

| 2.5 | Performance results of generated code on CPU                               | 47 |

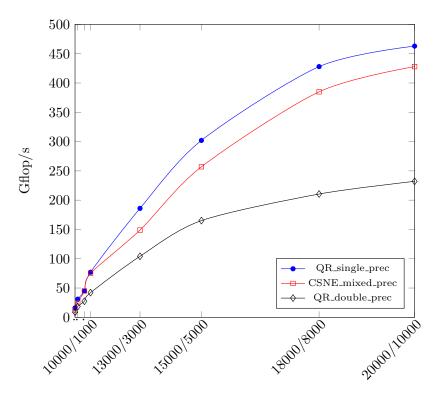

| 2.6 | Performance results of generated code on GPU                               | 50 |

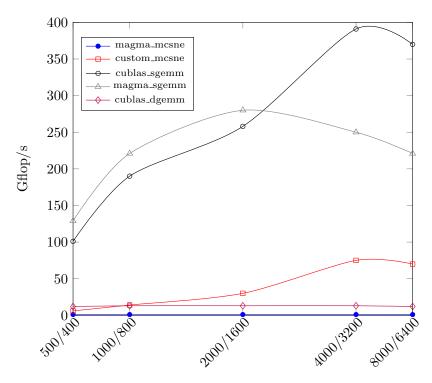

| 2.7 | Performance results on the Tegra X1 GPU                                    | 50 |

| 3.1 | Feature set comparison between $NT^2$ and similar libraries                | 55 |

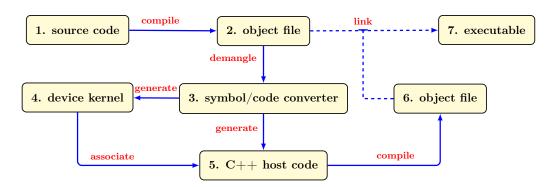

| 3.2 | Two phase compilation for device code generation                           | 58 |

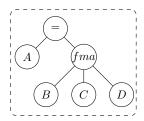

| 3.3 | Triad kernel transform AST                                                 | 60 |

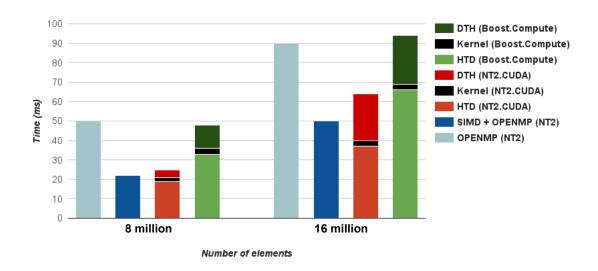

| 3.4 | Black and Scholes Performance Comparison (in ms)                           | 66 |

| 3.5 | Performance comparison on Tegra X1 with NT <sup>2</sup> (time in ms)       | 67 |

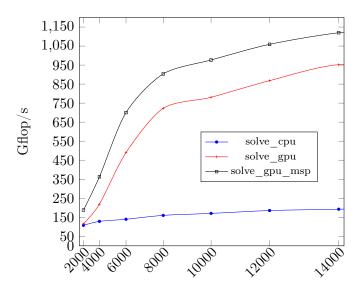

| 3.6 | Performance comparison of $NT^2$ linear solve (in $Gflop/s$ )              | 69 |

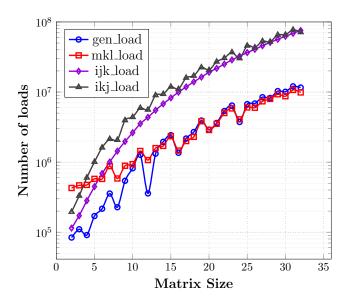

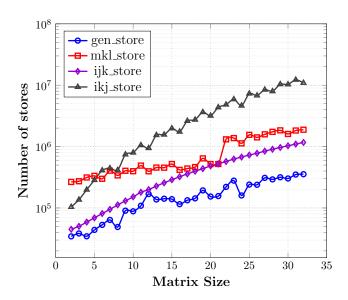

| 4.1 | # of load instructions                                                     | 83 |

| 4.2 | # of store instructions                                                    | 83 |

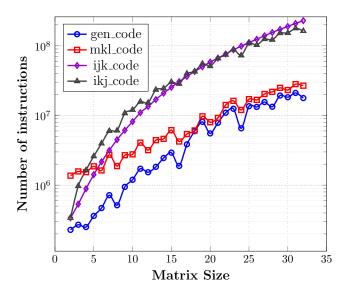

| 4.3 | Total CPU instruction count                                                | 84 |

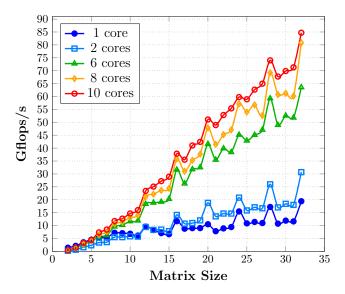

| 4.4 | Effect of the number of CPU cores                                          | 85 |

| 4.5 | Effect of the NUMA memory management                                       | 87 |

| 4.6 | Experimental results of the matrix-matrix multiplication on $\mathrm{CPU}$ | 88 |

| 4.7 | Experimental results of the matrix-matrix multiplication on the Tegra      |    |

|     | X1                                                                         | 89 |

| 4.8 | GPU performance on K40                                                     | 89 |

# Introduction

In recent years, architectures and programming languages have gone through major changes and diversification. The constant need for more computational power and more generic software has been the driving force behind these changes. Solving linear systems of equations Ax = b is part of many computational applications leading to a vast amount of research. The development of dense linear algebra has gone in hand with the evolution of computer languages and architectures. The High Performance Computing landscape has gone through many changes with the development of multicore processors and accelerators. One can safely predict that this trend will continue as current architectures are at a crossroad with the limits being reached for the lithography process. At the same time, computer languages have started to diversify with a focus on high level language concepts and functional programming paradigms. Recent languages such as Scala, Dotty, Rust or modern C++ are prime examples of this new direction. Such languages are also starting to become standard in High Performance Computing (HPC) to develop scalable and robust softwares. In this PhD thesis, we present a method of high level programming that takes into account the features of heterogeneous architectures and algorithmic properties to build numerical libraries.

The issues we consider throughout our work are related to software design and optimization for heterogeneous architectures. Software has historically being designed around solving problems for specific architectures, which limits portability and reuse. We propose an approach to develop generic interfaces that support architectural extensions. As the programming model can vary tremendously depending on the hardware, being able to give specifications when necessary and properly categorize hardware for code reuse is essential. This requires high level programming techniques that cannot be found in every language. The concept called Domain Specific Embedded Languages (DSEL) relies on a generic programming language that is flexible and expressive enough to enable the development of a sub-language with a definite syntax. This technique is known to be used in the languages mentioned above. In our work, we employ such programming techniques to design an architecture aware solver for dense linear systems. The resulting codes have been incorporated into a C++ library called NT2 <sup>1</sup>. We also consider the issues around batched computations and tensor contractions. This work is done outside of the NT2 library. A detailed explanation on how to develop a simple high level memory container without relying on current software is given. We then develop an optimized matrix-matrix product for small sizes using a tuning approach. In our benchmarks, computations on the GPU are run using the IEEE 754 compliant mode [138] for arithmetic operations and with CUDA ECC activated.

<sup>&</sup>lt;sup>1</sup>NT2 is available at http://github.com/jfalcou/nt2

This manuscript is organized as follows:

In Chapter 1, we present the background for our work. First, we consider the evolution of some numerical libraries and describe how architectures and programming languages have influenced them. Secondly, we discuss the main algorithms to solve dense linear systems and how to use them in the most popular HPC libraries. Then, we give a general description of current architectures and the main programming tools and techniques available. This includes low-level architectural tools that require expertise to properly program the hardware and high-level programming techniques to make abstraction of such problems. Then, we present the programming language and library we use throughout most our work.

In Chapter 2, we present our method to design a high level programming framework to generate dense linear algebra software. We start by giving a software context as there are several approaches to such a problem. Then, we present the code generation techniques that we for our CPU/GPU programming model. This model will then enable the development of a dense linear solver that can support hybrid architectures. We illustrate our approach with a least squares solver based on semi-normal equations for CPU, GPU and Integrated Graphic Processors (IGP) that cannot be found in state of the art libraries.

In Chapter 3, we extend the work described in Chapter 2 by proposing a multistage programming approach. We give a detailed background on related work and libraries available in C++ to solve the code portability and support problems. Then, we explain the process behind our multi-stage approach in C++ and how we have implemented it into the NT2 library. We test our approach with experiments on the Black & Scholes algorithm for GPU and IGPs and by applying our multi-stage approach to the work described in Chapter 2.

In Chapter 4, we investigate how to apply high level programming techniques to batched computations and tensor contractions. We start by explaining how to design a simple data container using modern C++14 programming techniques. Then, we study the issues around batched computations, memory locality and code vectorization to implement a highly optimized matrix-matrix product for small sizes using SIMD instructions. By combining a high level programming approach and advanced parallel programming techniques, we show that we can outperform state of the art numerical libraries.

The main contributions of this PhD thesis can be summarized as follows:

- We propose an architecture aware binding between  $NT^2$  and LAPACK/–MAGMA based on type tags to dispatch between the different architectures and runtime back-ends in an extensible way.

- We provide an implementation of *linsolve* (in reference to the MATLAB routine)

4 Introduction

that takes into account both hardware and algorithmic features to select and generate at compile time the proper LAPACK/MAGMA routine from the high-level C++ code, mapping over 160 kernels.

- We present a multi-stage approach to alleviate the host/device programming model with a cost model for offloading code. This provides adaptable strategy to generate CUDA kernel directly from a single C++ source file containing NT<sup>2</sup> statements.

- Our method takes advantage of modern C++ design for hybrid computations and interface development without relying on current software.

- We describe a strategy using performance analysis based on hardware features and counters to implement efficient algorithms on specific architecture. This work is based on the implementation of a small batched matrix-matrix product that can perform better than state of the art libraries.

# The issue of adapting numerical libraries to parallel architectures

| Contents | s     |                                                                  |           |

|----------|-------|------------------------------------------------------------------|-----------|

| 1.1      | Higl  | h level Programming for Scientific Computing                     | 7         |

| 1.2      | Solv  | ring dense linear systems                                        | 8         |

|          | 1.2.1 | LU factorization                                                 | 9         |

|          | 1.2.2 | QR factorization                                                 | 11        |

|          | 1.2.3 | Solvers in LAPACK and MAGMA                                      | 12        |

| 1.3      | Arc   | hitectures: Design and evolution                                 | <b>15</b> |

|          | 1.3.1 | SIMD extensions                                                  | 15        |

|          | 1.3.2 | Multicore systems                                                | 16        |

|          | 1.3.3 | Graphics Processing Units (GPU)                                  | 17        |

|          | 1.3.4 | Accelerated Processing Units                                     | 19        |

| 1.4      | Prog  | gramming tools and techniques                                    | <b>20</b> |

|          | 1.4.1 | Low-level programming tools                                      | 21        |

|          | 1.4.2 | Domain Specific Languages                                        | 24        |

|          | 1.4.3 | Domain Specific Embedded Languages                               | 25        |

|          | 1.4.4 | Multi-stage programming                                          | 26        |

| 1.5      | Con   | sidered language and library                                     | <b>26</b> |

|          | 1.5.1 | $C++$ language and programming techniques $\ldots \ldots \ldots$ | 26        |

|          | 1.5.2 | The $NT^2$ library                                               | 27        |

| 1.6      | Con   | elucion                                                          | 20        |

Parallelism in todays computer architectures is ubiquitous whether it be in supercomputers or small portable devices such as smartphones or watches. While computers hardware is evolving, computing power as expressed by Moore's law is still the incentive for all manufacturers. If frequency scaling has been a temporary solution, power dissipation and the increasing complexity in CPU design has lead manufacturers to develop more sophisticated architectures. These new architectures that allow to increase the computational power vary from CPU multicores to GPUs, or even integrated system-on-chip (SOC). Exploiting the full performance of such systems for numerical problems has become very challenging.

In order to take fully advantage of these new architectures, software libraries are developed to give user access to efficient linear algebra computations. The first major numerical libraries to appear include the Scientific Subroutine Package by IBM [72] in 1968, the Basic Linear Algebra Subprograms (BLAS [41]) or the Linear Algebra Package (LINPACK [42]) in 1979. Each of these packages were already implemented using some form of modular programming for better flexibility. Since then, architecture specific libraries for dense linear algebra have been developed such as LAPACK [6] for cache-based CPUs, ScaLAPACK [21] for distributed architectures, PLASMA [126] for multicores introducing tiled algorithms, data layouts and more recently MAGMA [12, 127] for accelerator-based architectures with GPUs or Xeon Phi.

These evolutions have gone in hand with programming techniques and languages. As we go back, LINPACK was written in Fortran 66 and LAPACK in Fortran 77. The more recent libraries were developed in C for PLASMA and C++ for MAGMA. In each new library the level of abstraction has been raised by using generic programming techniques. However, due to retro-compatibility concerns and the need to maintain a similar interface for the routines, the use of high level programming techniques is still very limited. Moreover, with the increasing parallelism and heterogeneity as well as the ever increasing data-communication cost, the algorithms were completely modified and redesigned to take advantage of each new architecture. The disparity between these libraries that target different architectures illustrates one of the major issues in designing optimized linear algebra software.

Parallel architectures are essential for scientific applications due to the high computing power they provide. Using efficiently these architectures is a difficult task due to the diversity of the hardware and the large amount of software solutions. Algorithms for CPU are still evolving to better adapt to architectures. For examples, the ReLAPACK [105] library has been developed using recursive programming techniques and can outperform LAPACK. It is in this context that we place our work. We focus on architecture aware software design for scientific computations.

In this chapter, we give an overview of the different architectures and programming techniques that are the premises for our work. After explaining why high level programming matters in Section 1.1, we present the algorithms and solvers for dense numerical libraries in Section 1.2. We then detail in Section 1.3 the different architectures and the impact they can have on the different algorithms. Following this, we present the programming tools and techniques in Section 1.1 that are used to develop high level libraries. Finally, we discuss in Section 1.5 about the language and library we used for our work.

## 1.1 High level Programming for Scientific Computing

The evolution of semiconductor technology is dramatically transforming the balance of future computer systems, producing changes at every level. From the point of view of numerical libraries, and the myriad of applications that depend on them, having more computational power allows to work on bigger simulations. These simulations can take up to months of continual computation depending on size of the problem. For this reason, having robust frameworks has become essential.

Developing fast applications in a reasonable amount of time requires a multi-disciplinary effort incorporating Domain Specific Languages, code generation and optimization techniques, domain science and application-specific numerical algorithms. As computational power and architectures are growing each year, it has now become a major concern to properly design libraries. In 2008 the first Petaflop machine entered the Top 500 while a research article was already explaining the challenges for ExaScale computing [18] and the emerging architectures. Modularity is now one of the main concern when writing software frameworks. Modern software such as GEANT4, a simulation toolkit for simulating the passage of particles through matter [4], or ROOT [23], for High Energy and Nuclear Physics, are developed using high level languages like C++ and can integrate other languages such as Python or R.

Exploring the use of accelerators as a general purpose co-processor to increase the computational power has been an active research field since the release of the CUDA language in 2007. Dedicated libraries for such architectures have emerged such as MAGMA, CUBLAS by NVIDIA<sup>TM</sup> or ACML by AMD<sup>TM</sup> but these are architecture specific. The MAGMA library exists in different versions depending on the hardware vendor. For major frameworks such as GEANT4, we can find research studies explaining how to implement algorithms for new architectures such as Xeon Phi [115]. These changes require advanced methodologies to compile and execute any scientific program. The article also shows that applications need to be heavily tuned to increase performance. The scientific community has a wide range of domains that require dedicated scientific applications to solve the programming challenges. Having an adaptable library does not need to be reimplemented for each new architecture is one of the main challenge of Scientific Computing.

## 1.2 Solving dense linear systems

Many scientific applications whether dense or sparse require at some point to solve a linear system of equations Ax = b. Examples range from fields such as Fluid Dynamics or Electromagnetism using Boundary Integral equations to tensor-based simulations [80]. Due to this, linear algebra algorithms must be robust, accurate and scalable to fulfill the needs of High Performance Computing.

This notion of numerical stability [69] plays a crucial role in designing algorithms as the result obtained by a numerical algorithm does not correspond to the solution of the problem in exact arithmetic. The different sources of errors may come from the input data of the algorithm, which may be caused by prior computations or measurement errors, which are themselves limited to the machine precision currently under the IEEE 754 norm [77]. Also, errors may be caused by approximations made

by the algorithm. Depending on the desired accuracy, several algorithms can be chosen to solve a linear system.

We can find two major approaches to solve linear systems: direct or iterative methods. A direct method uses a finite sequence of operations to provide an exact solution x if there are no rounding errors. The common method used to solve such systems is called Gaussian elimination. It consists in adding the coefficients of one equation to the others in order to eliminate a variable and continue this process until only one variable is left. Iterative methods start with an approximation of the solution  $x^0$  and successively compute a sequence of approximations  $x^i$  to improve the solution. In our work we focus on direct methods which are generally used to solve dense linear systems. Direct methods provide higher numerical precision and a good granularity of computations making it easier to exploit the latent parallelism. We note the main decompositions that exist [57]: LU, Cholesky, QR, SVD, LDL<sup>T</sup>.

- LU: Decomposes a general matrix A as  $L \times U$  where L is unit lower triangular and an U is upper triangular (about  $2 \times n^3/3$  flops).

- Cholesky: A symmetric positive definite (SPD) matrix A is factored as  $A = LL^T$  where L is lower triangular (about  $n^3/3$  flops).

- QR: An m-by-n matrix A is factored as A = QR with Q an m-by-m orthogonal matrix and R an m-by-n upper triangular matrix  $(2n^2(m-n/3) \text{ flops})$ .

- SVD: Decomposition of an m-by-n matrix A as  $A = U\Sigma V^T$ , U an m-by-m orthogonal matrix,  $\Sigma$  an m-by-n diagonal matrix (where the diagonal contains the singular values of A) and V an n-by-n orthogonal matrix V (the cost is about  $mn^2$  flops to compute  $\Sigma$ ).

- $LDL^T$ : factorization (using symmetric pivoting) is  $PAP^T = LDL^T$  where P is a permutation matrix, A is a symmetric indefinite square matrix, L is unit lower triangular and D is block-diagonal, with blocks of size  $1 \times 1$  or  $2 \times 2$  (about  $n^3/3$  flops).

#### 1.2.1 LU factorization

The LU factorization [57, p.111] is a modified Gaussian elimination without pivoting that decomposes a nonsingular matrix A into a lower triangular matrix, and an upper triangular matrix U. The number of floating point operations of the LU decomposition for a square matrix n is about  $2n^3/3$ . For dense matrices, the LU factorization is usually performed in place. This means that the output factors L and U overwrite the matrix A during the factorization.

#### Algorithm 1 LU factorization in place, no pivoting

```

Input: A is n \times n matrix

1: for k = 1 : n - 1 do

for i = k + 1 : n \ do

2:

A(i,k) = A(i,k)/A(k,k)

3:

end for

4:

for i = k + 1 : n \text{ do}

5:

for j = k + 1 : n \text{ do}

6:

A(i,j) = A(i,j) - A(i,k) * A(k,j)

7:

end for

8:

end for

9:

10: end for

```

The LU factorization is generally implemented using pivoting strategies because there are several important issues that can appear without pivoting. For example, if a zero is found on the diagonal of the matrix, a division by zero will occur leading to a numerical error. Also, if there are elements of small magnitude on the diagonal, the factors will end up growing too much also leading to erroneous results. We note PA = LU, with P a permutation matrix, when using partial pivoting in LU factorization. The stability of Gaussian elimination can be measured with the growth factor [69]. The growth factor measures the ratio between the entries of the matrix after the elimination steps and the original entries. The growth factor of a square matrix A under Gaussian elimination is defined as:

$$g_n(A) = \frac{\max_{i,j,k} |a_{ij}^{(k)}|}{\max_{i,j} |a_{i,j}|},$$

where  $a_{ij}^{(k)}$  is the element of index (i,j) after the step number k of the elimination [78]. The most common pivoting strategy used is called partial pivoting. It consists in permuting the rows but not the columns to ensure that the pivot is the largest entry in its column. For a step j of the Gaussian elimination, partial pivoting permutes the rows such that  $|a_{j,j}| \ge |a_{i,j}|$  for all i > j. This guarantees that  $||L||_{\infty} \le 1$ . Its growth factor upper bound is  $2^{n-1}$  which can be reached for certain problems [53].

#### Algorithm 2 LU factorization in place, partial pivoting

```

Input: A is a n \times n matrix

1: for k = 1 : n do

2:

index \leftarrow k

for i = k + 1 : n \text{ do}

3:

if |A(i,k)| > |A(index,k)| then

4:

index = i

5:

end if

6:

end for

7:

swap rows k and index

8:

for i = k + 1 : n \text{ do}

9:

A(i,k) \leftarrow A(i,k)/A(k,k)

10:

end for

11:

for i = k + 1 : n do

12:

for j = k + 1 : n \text{ do}

13:

A(i,j) = A(i,j) - A(i,k) * A(k,j)

14:

end for

15:

end for

16:

17: end for

```

The drawback of pivoting comes from the communication cost due to the comparisons performed to find the pivot and to the resulting swap of rows. For a square matrix, the partial pivoting requires  $\mathcal{O}(n^2)$  comparisons. Other well know pivoting strategies are total pivoting ( $\mathcal{O}(n^3)$  comparisons) and rook pivoting ( $\mathcal{O}(1.5n^{3/4\log n})$  comparisons).

The LU factorization is a classical technique that is used with different implementations in high performance linear algebra libraries. We can find applications with different pivoting strategies, precision, with iterative refinement or even in mixed precision. For this reason, we have used the LU factorization and its various forms as an important part of our generic solver for dense linear systems that we are going to detail in Chapter 2.

#### 1.2.2 QR factorization

The QR factorization [57, p.246] decomposes a matrix A into the product of an upper triangular matrix R and an orthogonal matrix Q. This is the main method used to solve the least square problem which consists in finding a minimal solution to a system Ax = b. This means solving  $||Ax - b||_p$ , A being an m by n matrix, for a defined p. There are multiple methods to compute the QR factorization of a matrix. Here we will focus on factorization with the Householder transforms which can be found in numerical libraries. We will described in Chapter 2 how we implemented a versions of mixed-precision semi-normal equations based on this QR factorization.

During the QR factorization, applying the Householder transformations on the matrix A will remove every entry below the diagonal. By repeating this process n

times, we obtain the upper triangular matrix R such that :

$$H_n H_{n-1} \dots H_1 A = R.$$

We note the form of an orthogonal matrix computed durign the factorization as:

$$H = I - \frac{2}{||u||^2} u u^T.$$

If we set  $Q = H_1...H_n$ , we can then obtain A = QR which means we have  $Q^T A = R$ . Algorithm 3 illustrates the QR factorization as described by Golub using the house function [57, p.237].

#### Algorithm 3 HouseHolder QR in place, no pivoting

```

Input: A is a m \times n matrix

1: for k = 1 : n do

2: [v, \beta] = house(A(j : m, j))

3: v_j = [0...0, 0, 1, v_{j+1}^j .... v_m^j]^T

4: \beta_j = \frac{2}{1 + ||A(j+1:m,j)||^2}

5: A(j : m, j : n) = (I - \beta v v^T) A(j : m, j : n)

6: if j < m then

7: A(j+1:m,j) = v(2:m-j+1)

8: end if

9: end for

```

We note that this method is known to be numerically stable [139].

#### 1.2.3 Solvers in LAPACK and MAGMA

Solvers for linear systems can be found in LAPACK and MAGMA constitute the building blocks to write a generic library for dense linear algebra. The routines given in these libraries can be distinguished by the static properties of the matrix. These properties correspond to the structure of a dense matrix which are for instance general, band, symmetric, positive definite or tridiagonal. Other structures can be considered but they may require new implementations to be written. The more common class of linear systems correspond to general dense matrices. This study focuses on dense matrices which already cover a wide range of applications.

What we describe below is the guideline of the main algorithms that are implemented. This however does not represent the implementation since it will depend of the structure of the matrix and also the target architecture. LAPACK being for CPU, the implementation is more straightforward and matches the algorithms while MAGMA will tend to be more specific. Indeed, since MAGMA is designed for GPU, it is important that the transitions between CPU and GPU is smooth to ensure minimal communication cost.

#### 1.2.3.1 General solvers

The solver used in LAPACK/MAGMA for general linear systems (xgesv, the letter x indicating the precision, either real (s), double-real (d), complex (c) or double-complex (z); ge standing for general) is based on the LU decomposition with partial row pivoting. This technique, called Gaussian elimination with partial pivoting is implemented in most numerical libraries including LAPACK and MAGMA and is used in the LINPACK benchmark for the TOP500 list.

To solve the linear system Ax = b, we compute a factorization PA = LU with P permutation matrix, L lower triangular and U upper triangular. Then the solution x is computed by solving successively the triangular systems Ly = Pb followed by Ux = y.

#### **Algorithm 4** Solving Ax = b with LU factorization

- 1: Compute the factorization PA = LU with P permutation matrix, L lower triangular and U upper triangular.

- 2: Solve Ly = Pb.

- 3: Solve Ux = y.

- 4: Solution is x.

In the case of rectangular matrices, the routine **xgelsy** uses the QR decomposition of the matrix (possibly with column pivoting) to solve the linear least square problem [20]:

$$\min_{x \in \mathbb{R}^n} \|Ax - b\|_2$$

#### **Algorithm 5** Solving Ax = b with QR factorization

- 1: Compute the factorization A = QR with Q orthogonal matrix and R upper triangular matrix.

- 2: Form  $d = Q^T b$ .

- 3: Solve Rx = d by backward substitution.

- 4: Solution is x.

The interest of these factorizations is that we can reuse the obtained factors for other computations which can also be very expensive such as computing the condition number [69], or performing iterative refinement [38]. In the case of a square matrix, we will identify three types of solvers that are available in LAPACK and will mention others that can added. In the case of a rectangular matrix we can identify a unique solver, which is the routine xgelsy.

The first one is the routine **xgesv** to compute a solution using the LU factorization. This can be seen as the standard case when there is no particular information about the system. Other cases include iterative refinement and mixed precision.

#### 1.2.3.2 Iterative refinement

The second one is the routine xgesvx using iterative refinement which enables it to improve the accuracy of the computed solution. Iterative refinement is a method that produces a correction to the computed solution by iterating on it. Each  $m^{th}$  iteration in this process consists of computing the residual  $r_m = b - Ax_m$ , solving the new system  $Ad_m = r_m$ , and adding the correction  $x_{m+1} = x_m + d_m$ .

#### Algorithm 6 One iteration of iterative refinement

- 1: Compute the residual r = b Ax.

- 2: Solve the new system Ad = r.

- 3: Add the correction x = x + d.

This method is computationally more expensive but can provide better solution for ill-conditioned systems.

#### 1.2.3.3 Mixed precision algorithm

The third method is the solver dsgesv that uses mixed precision iterative refinement [10]. This method takes advantage of the fact that computing in single precision is in general much faster than computing in double precision. The factorization (most expensive part of the computation) is computed in single precision ( $\varepsilon_s$ ) (if the matrix is not ill-conditioned) and the solution is refined in double precision ( $\varepsilon_d$ ) using the classical iterative refinement method.

#### Algorithm 7 Mixed precision, iterative refinement

| 1: Compute $PA = LU$     | $(arepsilon_s)$ |

|--------------------------|-----------------|

| 2: Solve $Ly = Pb$       | $(arepsilon_s)$ |

| 3: Solve $Ux_0 = y$      | $(arepsilon_s)$ |

| do $k = 1, 2,$           |                 |

| 4: $r_k = b - Ax_{k-1}$  | $(arepsilon_d)$ |

| 5: Solve $Ly = Pr_k$     | $(arepsilon_s)$ |

| 6: Solve $Uz_k = y$      | $(arepsilon_s)$ |

| 7: $x_k = x_{k-1} + z_k$ | $(arepsilon_d)$ |

| check convergence        |                 |

|                          |                 |

These methods can be found in current open source libraries. There are also other interesting methods that can provide satisfactory performance. An example is a method that accelerates linear system solutions using randomization techniques [14], in which the system is modified by a multiplicative preconditioning based on Random Butterfly Transformations [104] that removes the need for pivoting (which is an expensive process). Another method is based on communication-avoiding algorithms that minimize the cost of pivoting [11, 63].

#### 1.3 Architectures: Design and evolution

#### 1.3.1 SIMD extensions

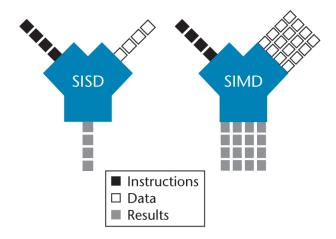

Single instruction multiple data (SIMD) architectures correspond to processing units that can perform an operation on multiple data simultaneously (see Figure 1.1). SIMD extensions are designed to help processors exploit the latent data parallelism available in many applications at a smaller cost than duplicating Arithmetic Logic Units (ALU).

Multiple constructors have implemented vector extensions. SIMD extensions started mostly with Sun Microsystems Visual Instruction Set (VIS) for the SPARC V9 [79] and Hewlett-Packard Multimedias Acceleration eXtensions (MAX) for the PARISC instruction set [84]. This lead other constructors to develop their own SIMD extension set.

Figure 1.1: SIMD concept

Motorola<sup>TM</sup> worked with Apple<sup>TM</sup> and IBM<sup>TM</sup> on the PowerPC architecture to develop the Altivec extensions [40] set. ARM<sup>TM</sup> introduced its first SIMD instruction set on ARMv6 which operated on 32-bit general purpose registers. Later on, ARM developed the Neon extension set for ARMV7-A with 64 bytes registers. Then, ARM extended Neon to 128 bits and added double precision computation. Intel<sup>TM</sup> introduced its SIMD extensions called streaming multimedia extensions (SSE) with the P5-based Pentium x86 processors. This first extension called MMX [106] used floating point registers instead of having specific vector registers which disabled scalar computations. Later on, they developed their first processors with dedicated vector registers (Pentium III) with 64 bytes registers. Since then, manufacturers have continued to increase the size of dedicated SIMD registers which now go up to 512 bytes vectors for Intel Xeon Phi coprocessors [26] (which corresponds to a line of L1 cache).

Exploiting the parallelism offered by these extensions is critical for high perfor-

mance computing as it can theoretically increased performance up to 8 times with 512 bytes registers for double precision operations. Using SIMD extensions can also increase the bandwidth. Linear algebra can benefit greatly from SIMD extensions as BLAS operations which are fundamental for most algorithm are vector based.

#### 1.3.2 Multicore systems

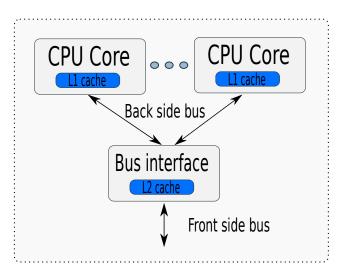

The processor manufacturers faced a technology limitation to their traditional approach of boosting clock speeds and increasing throughput due to power dissipation problems. This lead to the development of multicore architectures and hyperthreading as a solution which is a turning point in terms of software development. While constructors could increase the frequency in processors freely, the performance of a program would naturally increase which each new generation of processor. This went on until the end of the Intel Pentium 4 processors in 2006 with frequencies around 3.6 GHz. By then multicores were already available on the market but were not yet generalized. The common concept behind a multicore processor is to let each core have an L1 independent cache and put a shared L2 cache on the die which is the interface to the main memory. Figure 1.2 show a multicore systems with two levels of cache. Modern CPUs generally have two levels of cache in each core and a shared L3 cache. Having multiple CPU cores on the same die allows for a highly efficient cache coherent system at a much higher clock rate than if the signal had to travel off chip.

Figure 1.2: Multicore concept

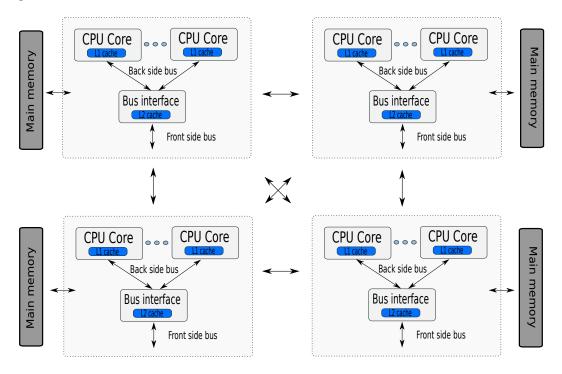

Most devices ranging from desktop computers and supercomputers to smartphones are based on a multicore design (see Figure 1.2). The number of cores can vary greatly depending on the solution going up to 22 cores on recent server based Intel Xeon processors family. Other parallelization techniques based on simultaneous multithreading (SMT) to improve the efficiency of superscalar CPUs can be found. As an example, Hyper threading (HT) consists in sharing resources by having two logical core for one single physical core. Another solution is the Non Uniform Memory Access (NUMA) architecture. Such systems are generally built around having multiple processors with each processor having its own memory bank (see Figure 1.3). Each processor is able to access the memory bank of the others but latencies will vary depending on the locality of each processor. To support this system, the operating system provides a virtual memory address space for all the processors in the NUMA node.

Figure 1.3: NUMA concept

#### 1.3.3 Graphics Processing Units (GPU)

Applications are becoming more demanding in workload and complexity as architectures become more powerful. CPUs have shown their limits in terms of computational power as they tend to be more general. This technology gap has led to the development of new architectures that are more specialized and can therefore provide more computational power for specific applications. GPUs are an example of a new type of architecture that has been emerging during the last decade.

A GPU is a specialized hardware to accelerate image display and processing. The first programming language for such architectures was released in 2007 by NVIDIA. The Compute Unified Device Architecture (CUDA) is a platform designed to work with scientific programming languages such as C, C++ and Fortran. CUDA has a

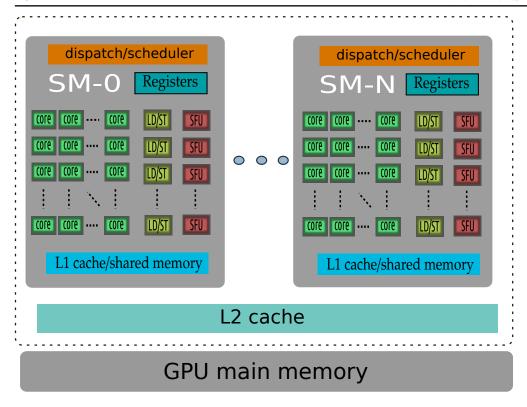

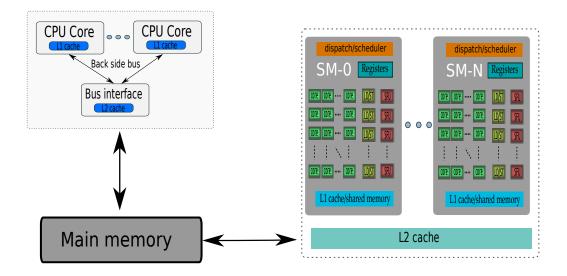

Figure 1.4: GPU Kepler based architecture

dedicated compiler called NVIDIA CUDA Compiler (NVCC) that supports C and a subset of C++. As of the November 2015 TOP 500 ranking, 75 machines are leveraging NVIDIA GPUs while only 55 were doing so in the June ranking. GPUs are now on the front scene of HPC as they are becoming increasingly important to improve the peak performance of systems. The other main vendor of GPU is AMD with its Accelerated Processing Platform (AMD APP).

GPUs architectures are very different from multicore CPUs and provide more computational power and better energy efficiency. The number of processing units available in a GPU is much higher than in a CPU (see Figure 1.4). A Tesla K40 has 2880 processor cores available but each runs at a lower frequency (745 GHz). Each of the cores can be seen as simple ALU that can only be used for computations. Cores are grouped together in what is called streaming multiprocessor (SM) with 192 CUDA cores for Kepler cards. Each SM has registers, an shared L1 cache and has a shared L2 cache between each SM with a maximum of 15 SM for Kepler cards. Similarly to CPUs, the number of cache levels on the GPU has grown to mitigate the high latency from the GPUs main memory.

Contrary to the CPU where data goes through each cache level for Intel processors, the data on the GPU does not necessarily stay at each cache level. Some data management therefore needs to be done to optimize data movement. The GPU

Figure 1.5: Work flow for a GPU

has a thread scheduler and control units in each SM(see Figure 1.4). The execution model of the GPU is based on deploying a large number of threads (in the order of millions) as they have no creation cost compared to a CPU. The scheduler will then distribute the threads minimizing the number of stall cycles. This creates a high parallel programming model where a high number of compute units will work in parallel. Communications with the CPU use the PCI express bus. The speed of the PCI bus can vary depending on the technology, with a maximum of 6 GB/s for PCI express gen 2 (16x) and 12 GB/s for PCI express gen 3. Depending on the application, the PCI express bus can be a bottleneck for memory-bound problems due to data transfers ( see Figure 1.6). With each new architecture generation, GPU architectures often go through many changes but manage to maintain the same programming model.

#### 1.3.4 Accelerated Processing Units

GPUs and accelerator based hardware are a major component of todays systems. However, using accelerators to their full potential can be impossible due to the limitations of the PCI express bus. Furthermore, GPUs are not stand alone processors and requires a CPU to function. This has lead to the development of System On Chip (SOC) hardware where a CPU and a GPU are combined on a single die. NVIDIA and AMD were the first manufacturers to develop this type of hardware with the NVIDIA Tegra brand in 2008 and AMDs Accelerated Processing Unit (APU) in 2011. Later on, Intel released its Integrated Graphic Processors for the

Intel core processors (Figure 1.8). As there is no official term for such hardware, we will refer to them as Integrated Graphic Processors (IGP). IGPs do not require a PCI Express bus as the CPU and GPU are on the same die (see Figure 1.6).

Figure 1.6: IGP architecture

As both hardware have a direct access to the main memory, the GPU has a higher memory bandwidth. The first implementations of IGPs by AMD did not have a unified memory system between the GPU and CPU. This meant that they could not access the same address space limiting the interactions between each processor. With it's second generation of IGP called Kaveri which was released in 2014, AMD implemented a zero-copy model where CPU and GPU can access the memory with the same address space. This means pointers can be freely passed between CPU and GPU, thus preventing actual deep copies. NVIDIA also released an IGP with zero-copy through the Tegra K1 and later on the X1. AMD IGPs are coupled with AMD CPUs while NVIDIA uses ARMs CPUs. It is important to note that current IGP have very poor support for double precision computations.

## 1.4 Programming tools and techniques

Section 1.3 described the current architectures without giving too much details about their programming models or the tools available for such platforms. In the next section, we are going to describe some of these tools and techniques often used to develop code for parallel architectures. Each tool will be described by its support for different architecture and expressiveness while techniques will explain how to build a tool for more expressiveness and architectural support.

Figure 1.7: Work flow for a zero copy IGP

#### 1.4.1 Low-level programming tools

#### 1.4.1.1 SIMD support

In section 1.3.1, we introduced the concept of SIMD extensions. Exploiting SIMD units in todays code is essential to reach the peak performance of a modern CPU. The most common method to exploit these extensions is by using the function intrinsics available. These functions are available in C but have been ported to other languages even web oriented ones such as JavaScript. The low level intrinsics in C are still used in every day programming and tend to be quite verbose. Depending on the size of the SIMD registers or the architecture, the intrinsics are also not the same. This causes some API problems and render complex the generalization of SIMD extensions. In Listing 1.1 we can see an example of the intrinsic for the multiplication of two 256 bits vectors.

```

__m256 a, b, c;

c = _mm_mul_ps(b,c);

```

Listing 1.1: Intel AVX2 single precision multiplication

The verbosity of SIMD instructions has been diminished in recent years and computational intrinsics such as addition, multiplication, etc.. can be replaced by its operator as seen in Listing 1.2.

Listing 1.2: Intel AVX2 single precision multiplication no intrinsic

On ARM NEON, the SIMD maximum size is 128 bit. It is therefore not possible to do the same operation as above but we can do a similar one with 128 registers. It is also possible to simply call the operator instead of the full intrinsic (Listing 1.3).

Figure 1.8: Intel's 3rd generation IGP architecture

```

float32x4_t a, b, c;

c = b * c;

```

Listing 1.3: ARM NEON single precision multiplication

In these examples we do not show the load and store operations needed to fill SIMD registers. For Intel processors, data also needed to be aligned on older processors to properly use SIMD extensions. On modern processors, unaligned load and store are quite sufficient to reach good performance most of the time as long as data doesn't cross cache lines. With the introduction of ARM supercomputer based system, recent studies [111] have shown how to improve energy efficient and design of HPC systems on low-power cores. Studying how these ARM based system can perform is therefore of interest.

Compilers for low level languages such as C, C++ can generate SIMD code through their auto-vectorization techniques. The programmer can write a simple code that will be translated to SIMD code during the compilation phase. GCC [100] is an example of a compiler using a vectorizer. It is also possible to use Just In Time (JIT) compilation to vectorize code with tools such as VaporSIMD [99] or use library based solutions such as Boost.SIMD [49] or VC [83]. The common problem with generating SIMD comes from how patterns are recognized. It is not always obvious how to vectorize a problem especially if data is not contiguous. Compiler can provide directives such as #pragma simd for ICC or #pragma GCC ivdep for GCC. These directives usually tells the compiler that their is no loop-carried dependencies which prevents consecutive execution of a loop with SIMD. Complex operations such as shuffle or intra-registers are hard for compiler to generate as they tend to be very specific. Some compilers also use SIMD extensions in their implementation of the standard library such as GCC.

#### 1.4.1.2 Multicore support

As we have seen in section 1.3.2 modern CPUs contain multiple cores on the same die. Most programming languages do no support multicore programming by default meaning the programmer must do the effort. We can still cite a language such as Chapel by CRAY which is available on Github. Chapel [25] is designed around multithreaded execution via high-level abstractions for data parallelism, task parallelism, concurrency and nested parallelism (see example in Listing 1.4).

Listing 1.4: Chapel Hello World

The main tools for parallel programming on multicore systems are Pthreads, OpenMP, TBB and MPI.

Shared memory multi-threading (pthreads) is an implementation of the POSIX 1003.1c Standard. It is based on a model where threads are spawned on the fly while each thread is given a task at its creation. The threads can then communicate through shared memory variables. The Pthread standard provides functions for thread synchronization - barriers, semaphores, and critical regions in its API. Pthread does not have a specific programming model and allows for task or data parallelism but requires a complex semantic and is error prone. It is a low-level explicit model where the programmer has to allocate threads, synchronize them, and then recompose them. Higher level implementation of Pthread can be found in programming language such as the C++11 std::thread.

**OpenMP** is a high level parallel programming model. It uses pragmas to add parallelism on a sequential implementation of an application. This requires the code section to be run in parallel to be dependency free between iterations. OpenMP also allows for task based parallelism to express dependencies. It uses a runtime library for thread management and scheduling techniques. The standard is constantly evolving and since OpenMP 4.0 supports extensions for accelerators based architectures.

Intel Thread Building Blocks (TBB) [108] is a C++ template library for data parallelism. It is based on the concept of tasks instead of threads which are higher level entities. TBB uses parallel skeletons constructs as building blocks. We note for example  $parallel_for$ ,  $parallel_reduce$ ,  $parallel_scan$  and  $parallel_sort$ . The task based abstraction is an efficient high level model and provide simple abstractions with the help of lambda expressions since C++11.

Message passing (MPI) is a popular programming model originally designed for distributed computing. It provides a low-level explicit model where each core of a processor can be addressed independently having its own memory pool. MPI is more of a task-based parallelism model but also supports data parallelism by deploying similar MPI processes on multiple data. Recent MPI standard have added special communicators for shared memory programming.

#### 1.4.1.3 Accelerator support

In section 1.3.3 we have explained how the GPU programming model is based on offloading data and using data parallelism. The standard programming tools used to program accelerators are CUDA and OpenCL.

CUDA is the programming language for NVIDIA graphic cards. It works for GPU as well as NVIDIA IGPs without having to change the device code. As explained before, the NVCC compiler supports a subset of the C++ language. To execute code on a GPU, the programming model includes a host code for the CPU and a device code which will be executed on the GPU. CUDA is an expressive language and simplifies the use of accelerators following the C++ standard evolutions. Unfortunately, it is not cross platform which can be a heavy restriction for portable code.

**OpenCL** is the portable solution for programming accelerators. It can work with CPUS and GPUs indistinctly but a single code cannot be highly efficient on both a CPU and a GPU. Similarly to CUDA, an OpenCL program has two parts. A kernel which will be executed on one or more OpenCL devices (similar syntax to CUDA), and a host program which is executed on the host. The Host code for OpenCL is very verbose as it is designed to work for every platform and several libraries try to alleviate this complexity. One of the main problem with OpenCL is that it is mostly C compliant and is therefore hard to mesh with high level programming without having to redesign around OpenCL.

#### 1.4.2 Domain Specific Languages

By definition, a Domain-Specific Language (DSL) is a computer language designed to fit a specific application domain. This is contrary to a general-purpose language, which is widely applicable across multiple domains and thereof lacks features for a specialized domain. These languages focus on simplifying specific tasks for developers by removing the complexity of a programming language. Adding this layer of abstraction helps developers to focus on the specificities of the domain described by the language, reducing the gap between domain experts and simple developers. DSL also have the effect of increasing the maintainability and ease the validation of codes.

There are a multitude of DSLs available ranging from domain such as editing documents to expressing physical problems. Tex, a markup language, is an example of a widely used DSL for document editing created by Donald Knuth in 1977. Tex

offers control over document formating with commands to help properly structure a text without having to focus too much on it. Other examples of well know DSLs are the Structured Query Language (SQL) to exploit databases or Hyper Text Markup Language (HTML) to create web pages.

In numerical computing, MATLAB<sup>TM</sup> [65], a multi-paradigm numerical environment, is the most popular DSL. The original purpose of MATLAB what to ease the use of the advanced LINPACK library without having to know any FORTRAN. MATLAB is mainly focused on matrix manipulations by exploiting optimized libraries such as LAPACK for CPU while providing utility tools for function plotting and data management. It is also interfacing with other languages such as C, C++, Java, FORTRAN or Python.

DSLs are usually part of a developing environment as they cannot be used as stand alone. To implement a DSL, one needs to write a compiler/interpreter for its language as it is not part of a general purpose computing language. This is a heavy cost as developing a DSL require more than just writing a language and can often suffer from performance issues due to the lack of optimizations. Another approach that we use in our work is based on Domain Specific Embedded Languages (DSEL) that we describe next.

#### 1.4.3 Domain Specific Embedded Languages

Domain Specific Embedded Languages (DSELs) are a subclass of DSL that rely on an existing general-purpose language to host it. DSELs then reuse the host language syntax and tool ecosystem to be compiled or interpreted. This means inheriting from the languages constructs (structure, conditions, functions, etc) while adding primitives that allow programmer to have access to a higher level of abstraction. Differences and advantages of DSELs over DSL are discussed by Abrahams [3, p.226]

There are several forms of DSEL available in different languages. Javascript is in a sense an embedded language in an HTML page, while HTML is a DSL. In scientific computing, DSEL rely on a generic language that is flexible and expressive enough to enable the development of a subset language with a definite syntax. This technique is know to be used in languages such as Lisp, Haskell, SmallTalk, C++, Scala and more. It is not always possible to reproduce a specific syntax in a general purpose language and sometimes a symbol needs to be replaced. For example, in C++ it is not possible to reuse the colon operator (:) as defined in MATLAB. This is one of the main shortcomings of a DSEL with the fact that it must be implemented inside a library and cannot be added to a language. Designing a DSEL is however often easier as they reuse existing compiler and rely on domain dependent analysis to generate efficient code.

We will describe how we can design a DSEL in C++ using meta-programming techniques in Chapter 2. Our work will focus on building a generic solver for dense linear algebra with multi-architectural support.

#### 1.4.4 Multi-stage programming

Multi-stage programming (MSP) is another approach than DSL and DSEL to increase the expressiveness of a programming language. MSP is defined as a meta-programming technique which consists in writing a program that will be able to generate new code. This means the state of the program will be modified during the compilation phase by the code meta-programmed.

MSP is usually applied by adding specific language extensions to trigger a new compilation phase. As an example, MetaOcaml [125] is a multi-stage language based on Ocaml [86] with three basic constructs for runtime code optimization. It adds type code values and constructs to build them called quoting and splicing. The generated code with MSP can then be stored in a file or compiled and linked directly to a Ocaml program enabling run-time code optimization.

More recent adoptions of MSP for parallel computing include techniques like Lightweight modular staging (LMS) [112] in Scala. Instead of using quasi-quotation LMS is based on types and uses an environment for MSP. Similarly to DSEL, using MSP with a host language requires this language to be flexible enough to adapt to MSP. Other approaches include Language Virtualization [24] (base on LMS) or Terra [39] using language extensions for HPC in Lua.

We will describe our work on MSP in Chapter 3 based on the C++ language and the CMake tool for the multi-level code generation.

### 1.5 Considered language and library

#### 1.5.1 C++ language and programming techniques

Generic programming is a paradigm that aims at achieving reusable, adaptable libraries. Pioneered by Alexander Stepanov and David Musser, Generic Programming obtained its first major success when the Standard Template Library became part of the C++ Standard. The process followed in generic programming is to first find the similarities among different implementations of a same algorithm in the form of concepts [61], and then provide an abstraction that can match all of these implementations. Concepts are a subtle mix of constraints and axioms used to represent the problem. The constraints define the statically evaluable predicates on the properties and syntax of the system, while axioms state the semantic informations about the types requirements, providing a better understanding of the problem. This process, called lifting, is then repeated until the generic algorithm has reached a suitable level of abstraction, where it provides maximal re-usability without sacrificing performance:

- Step 1 : Find similarities among different implementations

- Step 2: Provide an abstraction that can match all of those implementations

- Step 3: Iterate until a satisfactory level is reached

Generic Programming and Concepts provide support for Concept Checking, which allows for a limited support of parametrized types constraints [118], simplifying error checking at compile-time. In C++, concepts are being studied to be integrated in the standard as extension to the template system. They have been published as an ISO Technical Specification ISO/IEC TS 19217:2015.

Generative Programming is about bringing the benefits of automation to software development. Following this paradigm, any complex software system can be broken down to a list of interchangeable components which tasks are clearly identified and a series of generator that combine components by following rules set by an a priori domain specific analysis. The application of generative programming to parallel programming and hardware synthesis can be seen as a way to leverage the classical limitations of classic, library based tools by encapsulating expertise at the source code level and not only at the binary level. One of the most classical techniques for generative programming is Template Meta-programming.

Template Meta-programming is a meta-programming technique in which templates are used by a compiler to generate temporary source code, which is merged with the rest of the source code and then finally compiled. The output of these templates includes compile-time constants, data structures, and complete functions. The use of templates can be thought of as compile-time execution. This technique is used by a number of languages, the most well-known being C++ [3], D [22], Haskell [116] and OCaml [124].

#### 1.5.2 The $NT^2$ library

${

m NT^2}$  [48] is a numerical computing C++ library implementing a subset of the MATLAB language as a DSEL. The work that we described in Chapter 2 and 3 are extensions for this library.  ${

m NT^2}$  simplifies the development of data-parallel applications on a large selection of architectures currently including multi-core systems [128] with SIMD extensions. Simply put, a MATLAB program can be converted to  ${

m NT^2}$  by copying the original code into a C++ file and performing minor cosmetic changes (defining variables, calling functions in place of certain operators).  ${

m NT^2}$  also takes great care to provide numerical precision as close to MATLAB as possible, ensuring that results between a MATLAB and an  ${

m NT^2}$  code are sensibly equal.

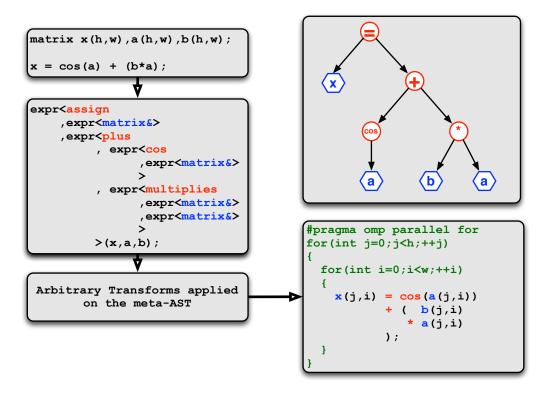

Internally,  $NT^2$  is designed to leverage the well known  $Expression\ Templates\ [132]$  C++ idiom to build at compile time a flexible representation of the abstract syntax tree of any C++ expression containing at least one  $NT^2$  component. This compile-time tree is then transformed in actual code to be executed on a parallel system. Contrary to other libraries based on the same technique,  $NT^2$  relies on BOOST.PROTO, an external  $Expression\ Templates$  system to handle the creation and transformation of Abstract Syntax Trees (AST) [98]. BOOST.PROTO allows us to replace the direct walk-through of the compile-time AST done in most

C++ *DSELs* by the execution of a mixed compile-time/runtime algorithm over the predefined AST structure generated by BOOST.PROTO (fig. 1.9).

Figure 1.9: Expression Templates in NT<sup>2</sup>

Finally, the other main difference between NT<sup>2</sup> and similar tools is the fact that architectural specificities of the generated code are handled by an execution model based on Algorithmic Skeletons[27]. Those skeletons simplify the extension of NT<sup>2</sup> for various hardware by separating the concerns of optimizing the AST code for different type of architecture. The main element of NT<sup>2</sup> is the table class. table is a template class that can be parametrized by its element type and an optional list of settings. Instances of table behave like MATLAB array and supports the same operators and functions. NT<sup>2</sup> covers a very large subset of MATLAB functionality, from standard arithmetic, exponential, hyperbolic and trigonometric functions, bitwise and boolean operations, IEEE related functions and of course linear algebra.

```

// Matlab: A = 1:1000;

table < double > A = _(1.,1000.);

// Matlab: B = A + randn( size(A1) );

table < double > B = A + randn(size(A1));

// Matlab: r = sqrt(sum((A(:)-B(:)).^2)/numel(A));

double r = sqrt(sum(sqr(A(_)-B(_))) / numel(A));

```

Listing 1.5: NT<sup>2</sup> RMSD Computation

1.6. Conclusion 29

Listing 1.5 showcases some NT<sup>2</sup> basic features including the mapping of the colon function (:) to the \_ object, various functions, a random number generator and some utility functions like numel or size.

In Chapter 2, we will explain how to build a hybrid programming model and how we have integrated ours inside  $NT^2$ . In Chapter 3, we will tackle the problem of MSP and explain how we can integrate it inside a C++ library using expression templates and the CMake tool.

#### 1.6 Conclusion

In this chapter, we have presented the linear algebra algorithms we will work with and their various versions in state of the art high performance dense linear algebra libraries. Then we have described the architectures and their different evolutions that have gone in hand with the development of new libraries to support these architectures.

We have also given a general description of the various programming tools available for these architectures. This is done as a reminder of how complex the architectural landscape and the various tools available is. We have then mentioned high level programming techniques to develop more generic and flexible software that can be adaptable to new architectures. Finally, we have described some of the C++ techniques we rely on and the library in which some of our code is implemented.

From what we have seen, it is clear that the diversity of architectures, which we have not all described, combined with the amount of libraries and programming languages available make for a very large landscape. In this manuscript, we will explain in detail techniques that can alleviate such problems. These techniques are implemented using the C++ language but are not exclusive to this language. As of now, C++ is a widespread high-level language in HPC. It is unclear which language will take this role in the future, but we can say that the programming techniques employed will have a place in it. It is in this context that we present our work.

In the next chapter, we will present one of our contribution in the form of a multi-architectural generic solver for dense linear algebra that is expendable to new architectures. We will show how to design simple GPU containers and a consistent memory model that will also be used in Chapter 3.

# High-level programming for dense linear algebra

| Contents | S                                       |                                                        |           |  |

|----------|-----------------------------------------|--------------------------------------------------------|-----------|--|

| 2.1      | Related Work                            |                                                        |           |  |

| 2.2      | Gen                                     | nerative programming for designing numerical libraries | <b>33</b> |  |

|          | 2.2.1                                   | Optimization approaches based on a configuration space | 33        |  |